重要性を増す後工程・先端半導体パッケージング技術

半導体チップの製造工程は大きく前工程と後工程の2つに分けられます。前工程はウエハ上に回路パターンを作り込む工程、後工程はウェハをダイ(ウェハを小片化しチップ化したもの)に切り分けパッケージングを行う工程です。

従来、半導体チップの高機能・高性能化はモノシリックのダイに、よりたくさんのトランジスタを集積することで実現してきました。また微細化・高集積化技術は主に前工程に関するものであったので、半導体製造技術における競争は長らく前工程の半導体製造プロセスにおけるトランジスタ微細化・高集積化技術が中心でした。

そしてトランジスタの集積密度は2年で2倍になるというムーアの法則があり、過去、微細化技術はこのムーアの法則に沿う形で進化を遂げてきました。

しかしながら近年ではシリコンウエハ上の微細加工技術は限界を迎えつつありその進化は鈍化しています。一方、半導体チップに対する更なる高機能化・多機能化の要求は留まることなく続いています。

そのため現在の最先端の半導体技術開発の現場では、前工程のみならず、後工程での半導体パッケージ技術を進化させることで高集積化を継続し、半導体チップの高機能化・多機能化の要求に応える取り組みが続けられています。

すなわち、従来は、微細化・高集積化に関しては、前工程が後工程より重要視される傾向にあったのが、最近では後工程、すなわち半導体パッケージ技術の重要度が非常に高まってきています。

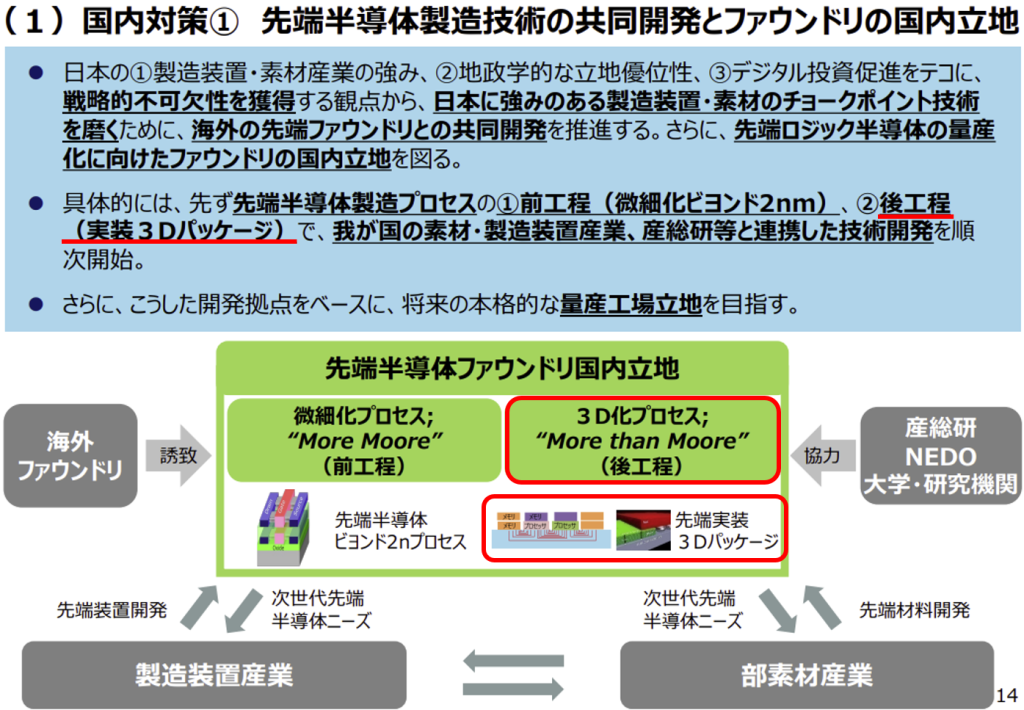

日本国内における半導体先端プロセス技術に開発は2010年代でほぼストップした状態になっていましたが、昨年(2021年)6月に経済産業省から出された半導体戦略では国内産業基盤の強靱化の一環として『先端半導体製造技術の共同開発とファウンドリの国内立地』が施策として打ち出されています。

半導体・デジタル産業戦略 半導体戦略(概略)資料より抜粋

この中では、海外ファウンドリ企業の誘致により国内の先端半導体製造基盤を強化するとともに、誘致したファウンドリ企業及び国内研究機関との協力関係により日本の強みである半導体製造装置産業と部素材産業を強化することが狙いとなっています。

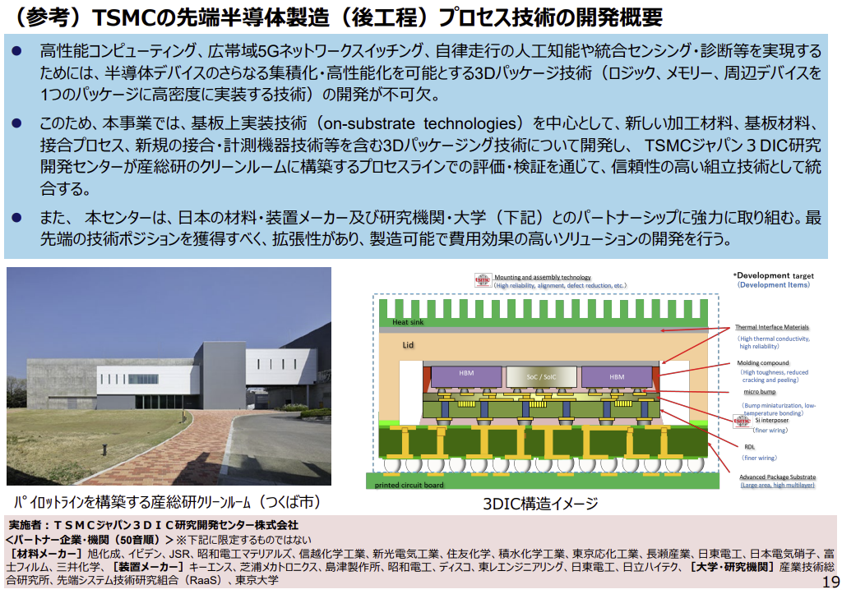

特に後工程については、半導体デバイスのさらなる集積化・高性能化に不可欠な3Dパッケージ技術開発を行うため、TSMCジャパン3DIC研究開発センター、産総研、及び国内装置メーカ・材料メーカによる共同研究が進められることになっています。

半導体・デジタル産業戦略 半導体戦略(概略)資料より抜粋

このように半導体製造技術における後工程の重要性の高まりは半導体製造装置メーカや電子材料メーカなど半導体サプライチェーンの中で競争力を強みを持つ日本企業にとっての大きなチャンスと考えています。また後工程に関する発明のクレームは前工程に比べると侵害立証のコストが低くなります。特許出願数の推移も含め、今後この分野でどのような進展があるか動向を注視していきたいと思います。