有機インターポーザ関連特許紹介

前回のコラムでは、シリコンウエハ上の微細加工技術は限界を迎えつつありその進化は鈍化しているため、後工程での半導体パッケージ技術を進化させることで高集積化を継続し、半導体チップの高機能化・多機能化の要求に応える取り組みが続けられていると述べました。

その中では異なる機能やサイズを有する複数のダイを同一のパッケージに高密度に実装することが求められています。またその背景の一つにはチップレットの思想に基づいた半導体チップ設計・製造の流れもあります。

複数のダイを高密度(つまり小面積で)に実装するには複数のダイをすべて積層したうえで、ダイ間の接続やダイとパッケージ基板との接続を行うのが最も効率的です。

しかしそのためにはアクティブな(機能を有するという意味)ダイに対して貫通ビア(TSV:Through Silicon Via)を設ける必要があり、製造コスト、電気信号の伝送特性、信頼性の面などで依然課題があり、HBM(High Bandwidth Memory)などハイエンドな製品では実用化されているものの、それ以外ではあまり実用化は広がっていない状況にあると思われます。またチップレット化されたヘテロジーニアスなマルチダイを全て積層化することは現実的ではないとも考えられます。

そのため、現在ではこの3D積層実装に加えて、複数のダイをインターポーザ上に平面的に密接に並べ、インターポーザを介してパッケージ基板と複数のダイを電気的に接続することで実装密度を上げる2.xD実装技術が実用化され、また更なる開発が続けられています。

この2.xD実装技術において重要な役割を果たす部材の一つがインターポーザです。

またインターポーザはその材料によっていくつかの種類が存在し、主要なものとしてはシリコンを用いたシリコンインターポーザ、有機ポリマーを用いた有機インターポーザ、ガラスを用いたガラスインターポーザがあります。シリコンインターポーザを用いたものを2.5D実装と、有機インターポーザを用いたものは2.1D実装と呼ばれることがあります。

2.5D実装のパッケージ技術は2012年頃からハイエンド用途の半導体デバイスですでに実用化されています。しかしながらシリコンインターポーザを用いる場合、ウェハー材料や製造コストが高価になるという問題点があるため、より安価な有機インターポーザを用いた2.1D実装も注目されています。

しかし有機インターポーザについても機械強度の面などで課題があり、依然、最適解を求めた研究開発が継続されています。

例えば先端パッケージ技術をリードするTSMCでは以下のような有機インターポーザの機械強度の補強する技術に関する特許(US11,282,756)を有しています。

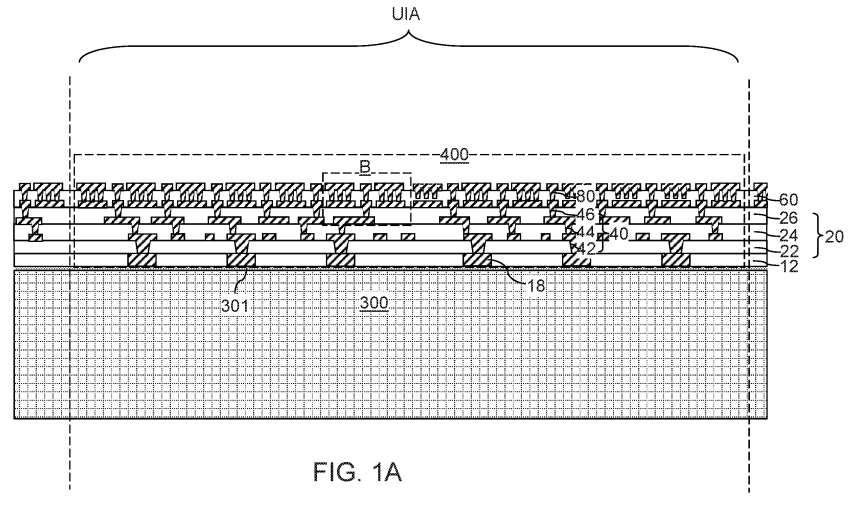

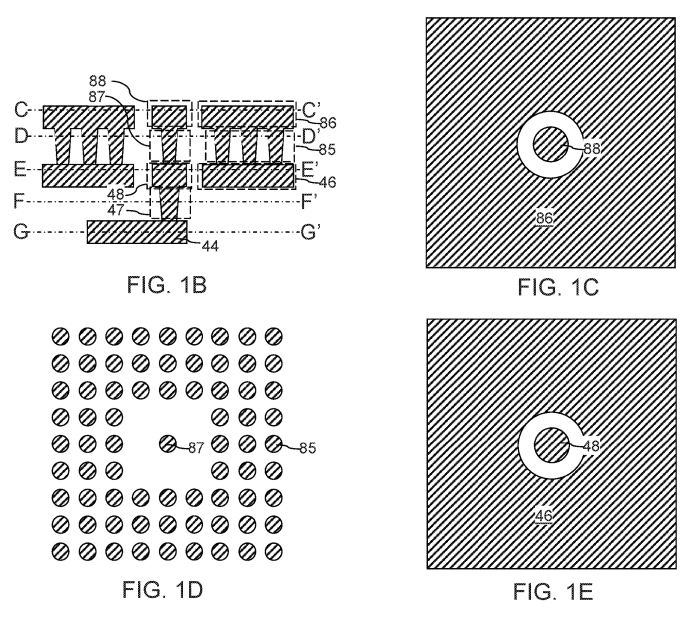

Fig.1A中の20は有機インターポーザであり、Fig.1A中の点線Bの部分を拡大した図がFig.1Bになります。またFig.1CはFig.1BのC-C’断面を、Fig.1DはFig.1BのD-D’断面を、Fig.1EはFig.1BのE-E’断面を示しています。

’756特許により、ダイ側のバンプ(88)及びそれに接続されるバンプ接続ビア(87)の周囲に金属シールド構造(86,85)を設け、ダイをパッケージ基板に接着するためのボンディング工程の際に有機インターポーザ(若しくはその内部に構成される再配線層)20に生じる応力を軽減できると考えられます。

今後も先端半導体パッケージの分野における有機インターポーザの動向に注視していきたいと思います。